【1】はじめに

トランジスタの登場(1947年)は、真空管時代を終わらせ、

その後の電子機器の小型化・高性能化を一気に進めました。

しかし、トランジスタを1個ずつ配線していた時代には、

・ 配線の複雑化

・ 信号遅延

・ コスト・信頼性の問題

といった課題が山積していました。

それを根本から変えたのが、集積回路(IC:Integrated Circuit)です。

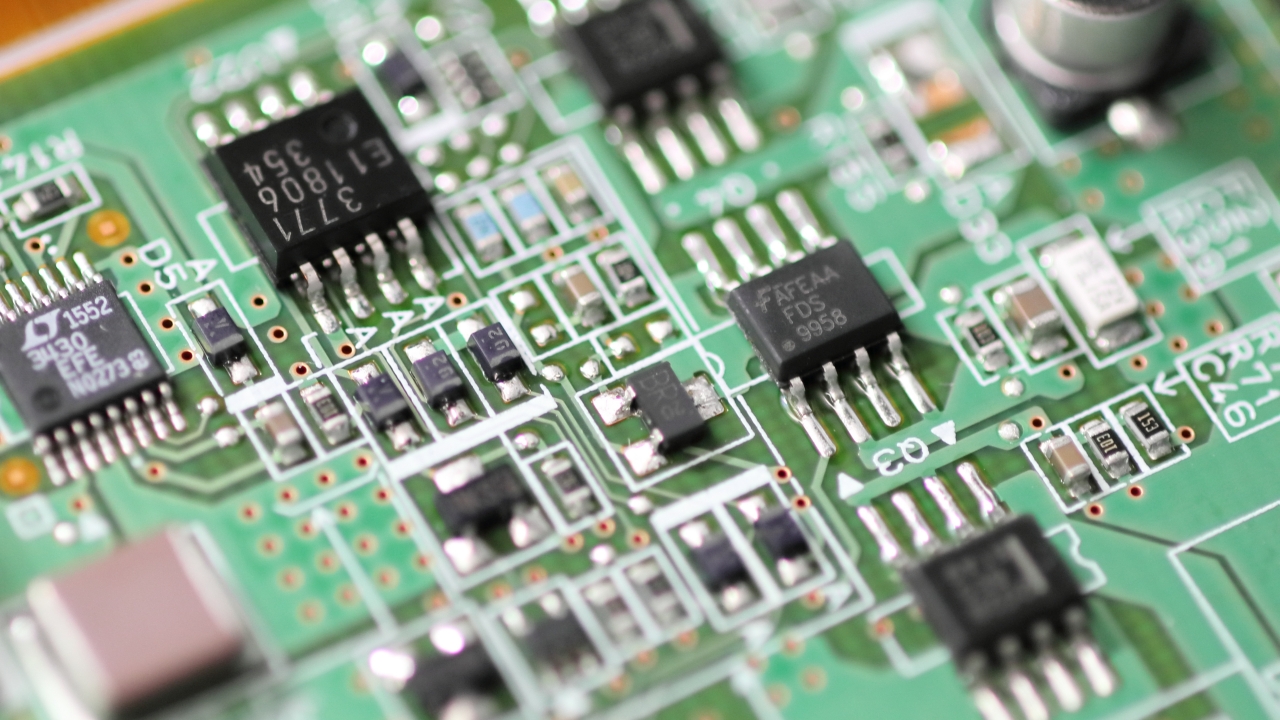

【2】集積回路(IC)とは

ICとは、「複数の電子素子(トランジスタ・抵抗・コンデンサなど)を、

1枚の半導体基板上にまとめて形成した回路」です。

つまり、電子回路そのものをチップ化したもの です。

これにより、信号の伝達距離が短くなり、速度・省電力・信頼性が飛躍的に向上しました。

【3】ICの誕生と初期の発展

● 1958年:テキサス・インスツルメンツ社のジャック・キルビーが最初のICを発明。

● 1959年:フェアチャイルド社のロバート・ノイスがシリコン基板上でICを実現。

これが、今日まで続く半導体集積技術の起点となりました。

初期のICはトランジスタ数が数十個程度で、

「SSI(Small Scale Integration)」と呼ばれていました。

【4】集積度の進化段階

半導体集積技術は、集積されるトランジスタの数に応じて分類されます。

● SSI(Small Scale Integration):数十個(1950〜60年代)

● MSI(Medium Scale Integration):数百個(1970年代初期)

● LSI(Large Scale Integration):数千〜数万個(1970年代後半)

● VLSI(Very Large Scale Integration):数十万〜数百万個(1980〜1990年代)

● ULSI(Ultra Large Scale Integration):数千万〜数億個(2000年代〜)

現在では、1チップに数百億個のトランジスタが集積されています。

【5】集積回路の種類

集積回路は大きく2種類に分類されます。

1.アナログIC:信号を連続的に処理する回路。

→ 代表例:オペアンプ、電源IC、センサー回路など。

2.デジタルIC:0と1の離散信号を扱う回路。

→ 代表例:ロジックIC、マイクロプロセッサ、メモリなど。

多くのシステムでは、これらを組み合わせた混載IC(Mixed Signal IC)が使われています。

【6】集積回路を支える技術要素

ICが成立するためには、以下の要素技術が不可欠です。

● 微細加工技術(リソグラフィ、エッチング)

● 不純物ドーピング技術

● 絶縁膜形成(酸化・CVD)

● 配線(メタル層形成)

● パッケージングと実装

これらが連動して、ナノメートル単位の構造を実現しています。

【7】LSI(大規模集積回路)の特徴

LSI以降では、単なる部品集積ではなく、機能集積が進みました。

1チップ内で演算、記憶、制御、通信などを同時に実現します。

例:

● CPU(演算)

● GPU(画像処理)

● DSP(信号処理)

● SoC(System on Chip:複合機能集積)

これにより、スマートフォン1台でかつてのスーパーコンピュータを超える性能が得られるようになりました。

【8】VLSI(超大規模集積回路)時代

1980年代に入り、CAD(回路設計自動化)が進み、

トランジスタ数が爆発的に増加しました。

VLSI時代には、次の技術革新が起こりました。

● 微細化プロセス(μm → nmスケール)

● CMOS化(低消費電力化)

● マルチレイヤ配線

● 自動設計(EDAツール)

これらの進歩が、ムーアの法則(18〜24か月で2倍)を現実にしたのです。

【9】現代の超高集積化(ULSI〜3D IC)

現在では、微細化だけでなく3次元構造による高集積化が進んでいます。

● TSV(Through Silicon Via)による3D積層

● Chiplet構造によるモジュール化

● Heterogeneous Integration(異種デバイス統合)

これにより、性能・省電力・設計自由度を両立させる新しい時代に入りました。

【10】今後の展望

今後の集積技術は「単純な微細化から、最適化と分業化へ」と進むと予測されます。

● 3D IC・Chiplet化による構造的拡張

● AI設計支援による最適レイアウト

● 量子デバイス・光集積回路との融合

● パッケージ内集積(2.5D/3D SiP)によるモジュール最適化

つまり、1枚のチップではなく、複数チップが協調動作する時代へと向かっています。

【11】まとめ

・ ICは「複数の電子素子を1つのチップ上に集積したもの」。

・ 集積度は、SSI → MSI → LSI → VLSI → ULSIと発展。

・ LSI以降は機能集積(SoC, CPU, GPU)に進化。

・ 現在は、3D構造・Chiplet・AI設計など“複合最適化時代”に突入。

【理解チェック】

1.集積回路(IC)の最大の利点は?

2.LSIやVLSIは何を意味するか?

3.これからの集積化の方向性は?

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。