【1】半導体製造とは何か

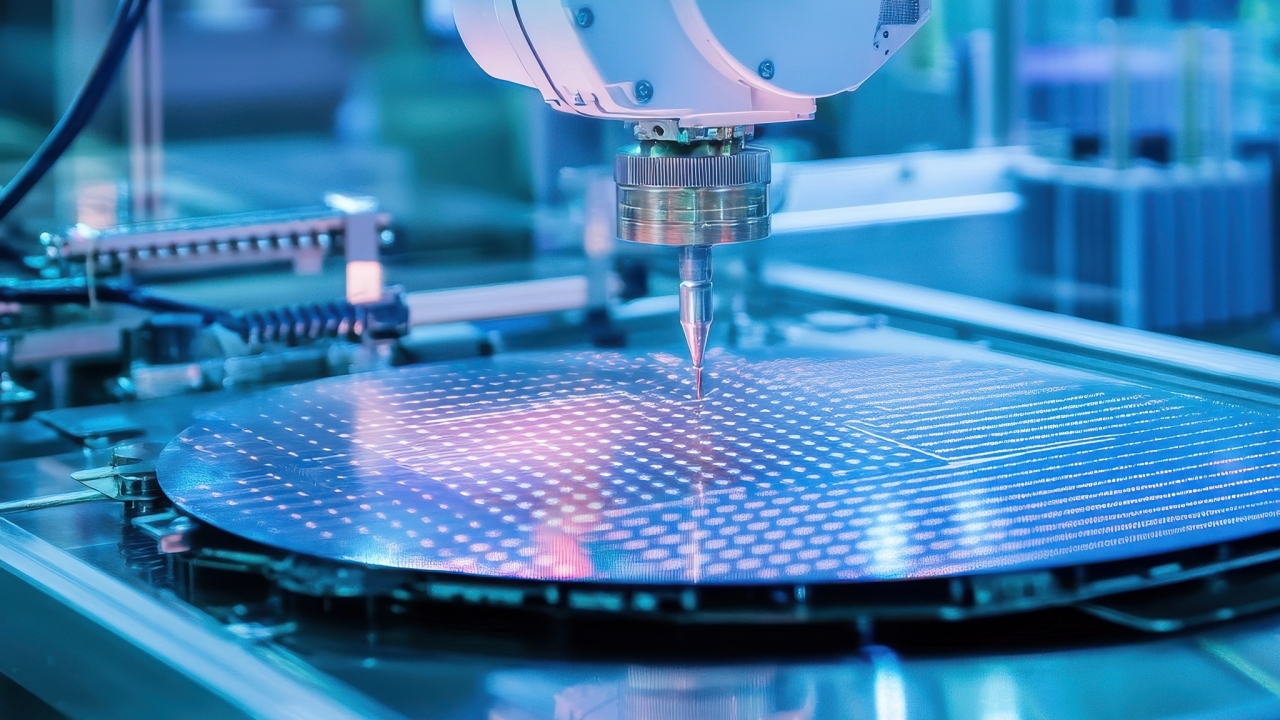

半導体製造とは、1枚のウェハから数百〜数万個のチップを作る超精密プロセスであり、

完成までに 1000〜3000の工程 を経ることも珍しくありません。

全体像は、次の2段階に大別されます。

● 前工程(ウェハ加工:トランジスタと配線を作る)

● 後工程(パッケージ:封止・実装・検査)

【2】前工程(Front-End:FEOL + BEOL)

前工程では、ウェハ上に

トランジスタ(素子)を作り、配線(回路)を形成します。

● FEOL(Front-End Of Line:素子形成)

MOSFET・FinFET・GAAなどのトランジスタ構造を作る工程。

例:酸化、成膜、露光、エッチング、イオン注入、アニールなど。

● BEOL(Back-End Of Line:配線形成)

トランジスタ同士を銅配線でつなぐ工程。

Low-k膜と金属配線を積層し、回路を完成させる。

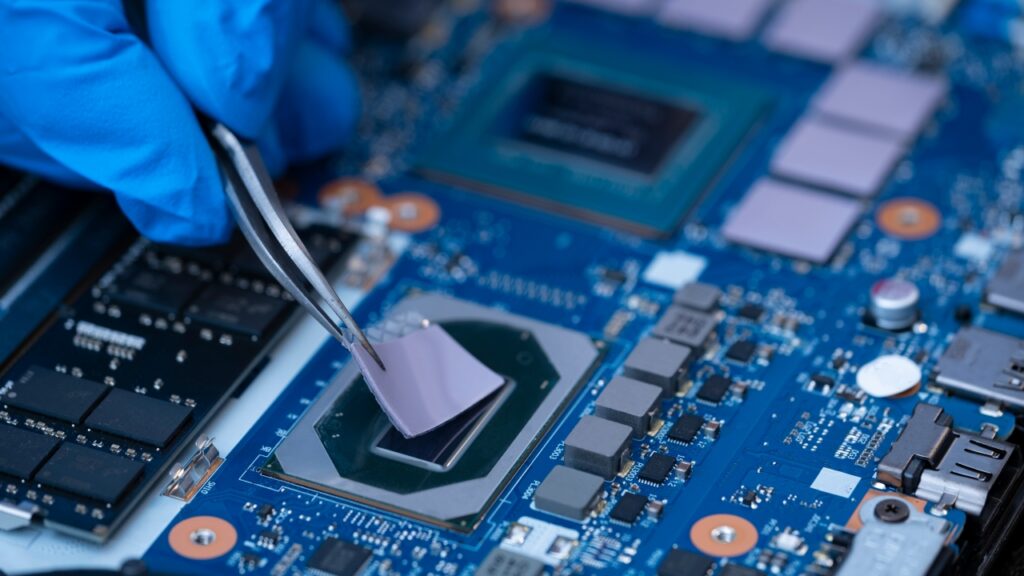

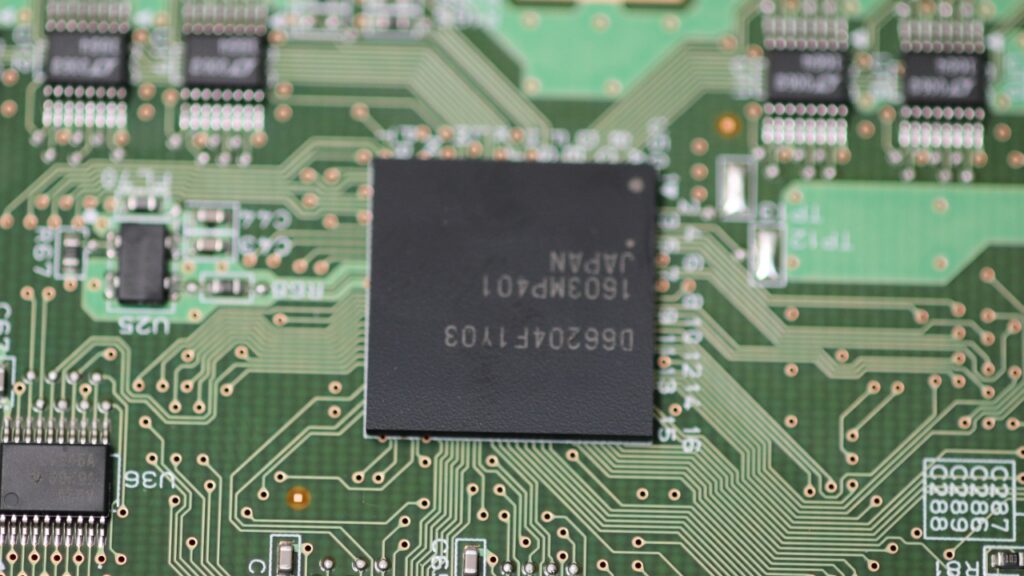

【3】後工程(Back-End:Assembly & Test)

後工程では、前工程で作ったウェハを

チップに切り分け、パッケージに封止し、最終テストを行う。

主な工程は以下:

● ダイシング(ウェハ切断)

● パッケージング(ワイヤボンド/フリップチップ)

● 基板への実装

● ファンクショナルテスト(FT)・Eテスト(E-Test)

ここでは、ウェハが出荷可能な製品へ仕上がる。

【4】製造プロセスの全体フロー

製造工程の流れをテキストで整理すると、次のようになります。

【前工程】

1.ウェハ製造(Si / SiC / GaN)

2.酸化膜形成

3.成膜(CVD / PVD / ALD)

4.レジスト塗布

5.露光(ArF / EUV)

6.現像

7.エッチング

8.レジスト剥離

9.イオン注入(ドーピング)

10.アニール(活性化)

11.CMP(平坦化)

12.配線形成

13.多層配線(BEOL)

【後工程】

1.ダイシング

2.パッケージング

3.実装(基板搭載)

4.電気テスト

5.出荷

半導体はこの中で、成膜 → 露光 → エッチング → 平坦化

のプロセスを何十回も繰り返すことで完成します。

【5】半導体製造の特徴

● (1)層を積み上げる「超立体構造」のものづくり

薄膜形成 → パターニング → 除去 → 平坦化の繰り返しで

立体的に回路を組み上げていく。

● (2)歩留まり(Yield)が最重要

微粒子や残渣、わずかな膜厚ばらつきが不良の原因になるため、

徹底したプロセス管理が求められる。

● (3)クリーンルームは製造の生命線

人間が最大の汚染源と言えるため、

Class 1〜1000レベルの徹底管理が必要。

● (4)巨大装置産業でもある

露光(ASML)、成膜・エッチング(東京エレクトロン、LAM、AMAT)など

世界の装置メーカーが重要な役割を担う。

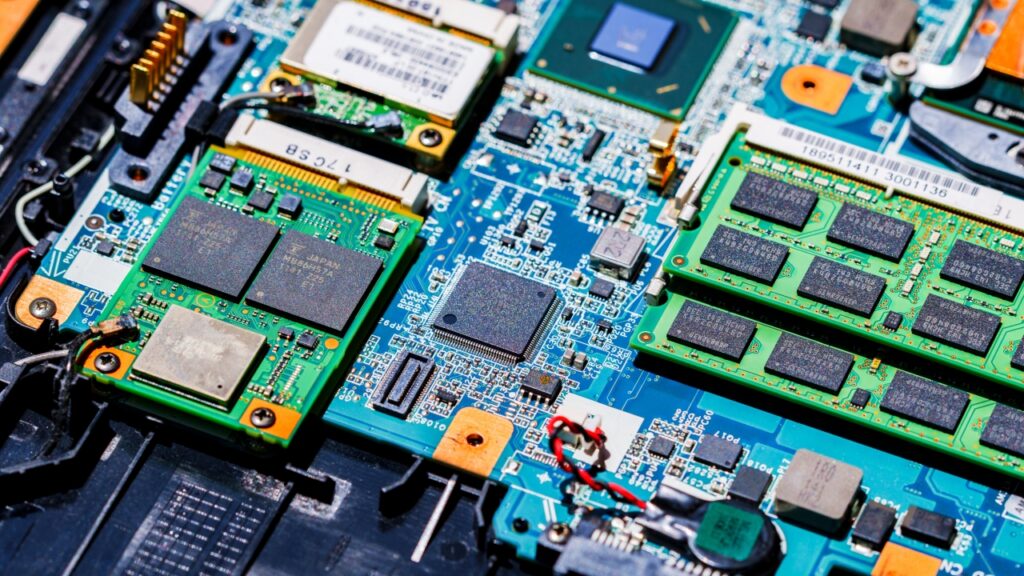

【6】FEOL・BEOL・後工程の関係

半導体製造は以下のように段階的に進む。

● FEOL(素子形成):MOSFETなどのトランジスタを作る

● BEOL(配線形成):トランジスタ同士を銅配線で接続

● 後工程(Assembly):チップ化・封止・検査

この3段階で、ウェハは製品へと仕上げられていく。

【7】まとめ

● 半導体製造は「前工程」と「後工程」に大別される。

● 前工程=トランジスタと配線の形成。

● 後工程=パッケージングと最終テスト。

● 工程全体では、清浄度・歩留まり・設備管理が極めて重要。

【理解チェック】

Q1. 半導体製造の工程は大きく何と何に分かれていますか?

Q2. FEOL と BEOL の違いを説明してください。

Q3. 半導体製造でクリーンルームが重要な理由は?

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。