【1】パッケージングとは何か

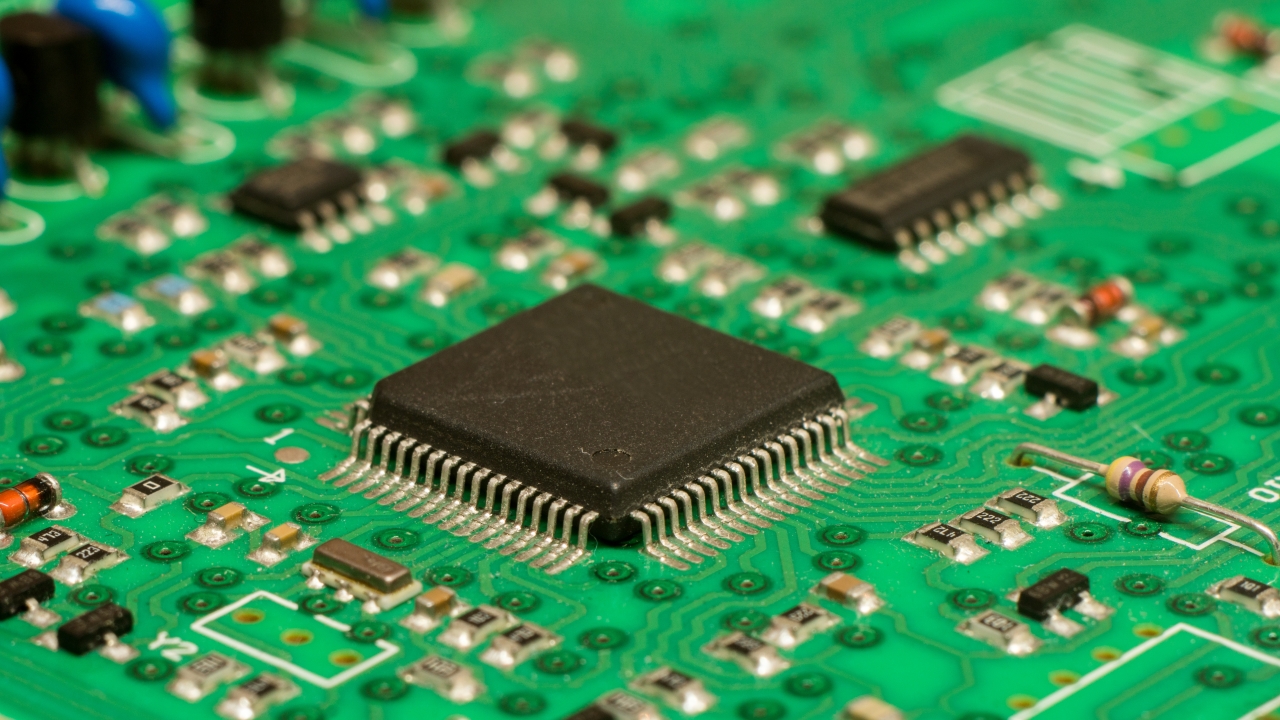

パッケージング(封止)は、前工程で完成したシリコンチップを使える状態に仕上げる工程。

目的は大きく3つ:

1.チップを外部環境から守る(湿度・衝撃)

2.電気的に外部と接続する(入出力端子)

3.熱を逃がして安定動作させる

つまり、「裸のチップ(Die)」を製品として機能させる最終加工」 にあたる。

【2】パッケージングが必要な理由

近年は微細化が進むほど、

● 薄い

● もろい

● 発熱が大きい

● 配線が密集

● 電流が増加 と難易度が急上昇。

そのため、パッケージングは、チップ性能を最大限引き出す第2の設計思想と言われる。

【3】主要なパッケージング方式

●(1)ワイヤボンディング(Wire Bonding)

昔から使われる標準方式。

チップ上のパッドとリードフレームを金線などで接続する。

特徴:

・ 安い・確実・成熟技術

・ メモリ、MCUなど量産向け

・ ただし配線長が長く高速信号には不利(遅延・ノイズ)

●(2)フリップチップ(Flip-Chip)

チップ上にバンプを形成し、裏返して基板に直接接続。

特徴:

・ 配線が短く高速

・ 熱を逃がしやすい

・ 多端子・高性能デバイス向け(CPU / GPU / ASIC)

・ コストや実装難易度は高い

ハイエンド半導体の標準方式。

●(3)BGA / QFN などモールド型パッケージ

樹脂で封止したコスト型パッケージ。

例:

・ BGA(Ball Grid Array)

・ QFN(Quad Flat No-lead)

・ SOP / DIP(古典的方式)

特徴:

・ 小型・安価

・ モバイル機器に最適

・ チップ単体は保護されるが熱は逃がしにくい

●(4)Fan-out / Fan-in パッケージ(FOWLP)

近年トレンドの高密度パッケージ。

■ Fan-out(InFO, eWLB)

チップの外側に配線を広げる方式。

特徴:

・ 薄型

・ チップサイズ以上に配線を展開

・ Apple Aシリーズなどに採用

■ Fan-in

チップ内に配線を収める方式。

スマホ用PMICなど、小型重視の用途で使用。

●(5)2.5D / 3Dパッケージ(CoWoS, HBMなど)

AI・データセンター時代の主役。

■ 2.5D(シリコンインターポーザ)

・ 複数チップを1枚のSiブリッジ上で配線

・ 代表例:TSMC CoWoS

・ HBM(高帯域メモリ)+ロジックの組み合わせが代表

■ 3Dパッケージ

・ TSV(Through Silicon Via)を使い、上下に積層

・ 距離が最短で高速

・ ただしコスト・熱対策が非常に難しい

AIサーバ向けGPUで爆発的に需要が伸びている。

【4】熱(Thermal)・EMI・信頼性の設計ポイント

パッケージングは 熱・電気・機械の総合技術 である。

代表的な課題:

●熱対策(Thermal)

・ 大電流化により発熱増加

・ TIM(熱インターフェース材料)

・ ヒートスプレッダ

・ 放熱基板(メタルコアなど)

●EMI(電磁ノイズ)

・ 高速化でノイズ干渉が増大

・ シールド構造が重要

・ 樹脂封止内部の金属粒子管理

●機械的信頼性

・ 温度サイクル

・ はんだクラック

・ ワイヤ断線

・ モールド樹脂の剥離

パッケージの信頼性が低いと最終製品全体の故障率が跳ね上がる。

【5】パッケージの材料構成

代表的な材料:

・ 基板(BT、ABF、セラミック)

・ はんだボール(SnAgCu系)

・ バンプ(Cu / Ni / Sn)

・ モールド樹脂(エポキシ)

・ アンダーフィル(フリップチップ用)

・ TIM(熱インターフェース材料)

材料開発は急速に進化しており、特にABF基板は半導体の戦略物資と呼ばれる。

【6】最新トレンド

・ HBM+ロジックの2.5D構造(AI時代の主流)

・ Chipletアーキテクチャ(AMD、Intel、Apple)

・ 熱拡散構造の複雑化

・ 樹脂の低誘電率化

・ ウォーターフリー工法

・ 超薄チップ向け応力制御技術

パッケージ技術が 半導体の性能を左右する時代 になっている。

【7】まとめ

・ パッケージングはチップを保護し、外部と接続する最終工程

・ ワイヤボンド・フリップチップが基本

・ Fan-out や 2.5D/3D は高性能向け

・ 熱・EMI・信頼性が大きな設計課題

・ AI・HPCで高密度パッケージの需要が爆発している

【理解チェック】

1.ワイヤボンディングとフリップチップの最大の違いは?

2.Fan-out パッケージがスマホ用途で人気な理由は?

3.HBMが2.5Dパッケージと組み合わせられる理由を説明してください。

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。