【1】装置技術が重要な理由

半導体製造は、材料 × プロセス × 装置 の掛け算で成り立つ産業。

その中でも装置は、

● 微細化(2nm→1nm)

● 3D構造(FinFET→GAA)

● 高アスペクト比(100:1以上)

● 新材料(High-k、Low-k)

● 高密度配線 などの要求を実現する最も重要な基盤。

技術進化の限界は、装置技術の限界で決まる と言っても過言ではない。

【2】EUV露光(Extreme Ultraviolet Lithography)

(1)EUVとは

EUVリソグラフィは波長13.5nmの光を使う露光技術。

従来のArF(193nm)より非常に短い波長であり、微細化の鍵を握る究極のリソグラフィ装置。

(2)EUVの構造と特徴

EUV装置は世界で最も複雑な装置の一つ:

・ レーザーでSn(スズ)をプラズマ化 → EUV光を生成

・ 反射率の低い光のため、すべて“反射光学系”

・ 反射鏡はMo/Si多層膜(100層以上)

・ 真空環境が必須

・ マスクも反射型(EUV mask)

1台 300〜400億円 と超高額。

(3)EUVの課題

・ マスク欠陥(Mask Defect)

・ Stochastic effect(確率的欠陥)

・ 光源出力不足

・ 露光スループットの限界

・ 高NA化による鏡面加工精度要求の上昇

特に確率的欠陥は、写真現像と同じように粒状ノイズが結果を左右する ため厄介。

(4)高NA EUV(0.55NA)

次世代の主役。

・ 解像度が大幅向上

・ 1nm台のパターニングに必須

・ しかし装置サイズは巨大化(高さ=バス2台分)

・ マスクブラー(Mask 3D Effect)が深刻化

IntelとASMLが初導入する予定。

【3】真空技術(Vacuum Technology)

微細加工はほとんどが真空下で行われる。

真空が必要な理由

● 気体分子の衝突を避ける

● 反応ガスの純度を上げる

● プラズマ安定性の向上

● 膜堆積の均一化

● 表面汚染の防止

真空ポンプ、配管、シール技術は非常に重要。

代表的なプロセスと真空の関係

● CVD → 低圧(LPCVD)

● PVD → 高真空

● ALD → 超高真空・精密ガス制御

● イオン注入 → 高真空

● EUV → 極高真空(10⁻⁶ Paレベル)

真空の品質が直接歩留まりに影響する。

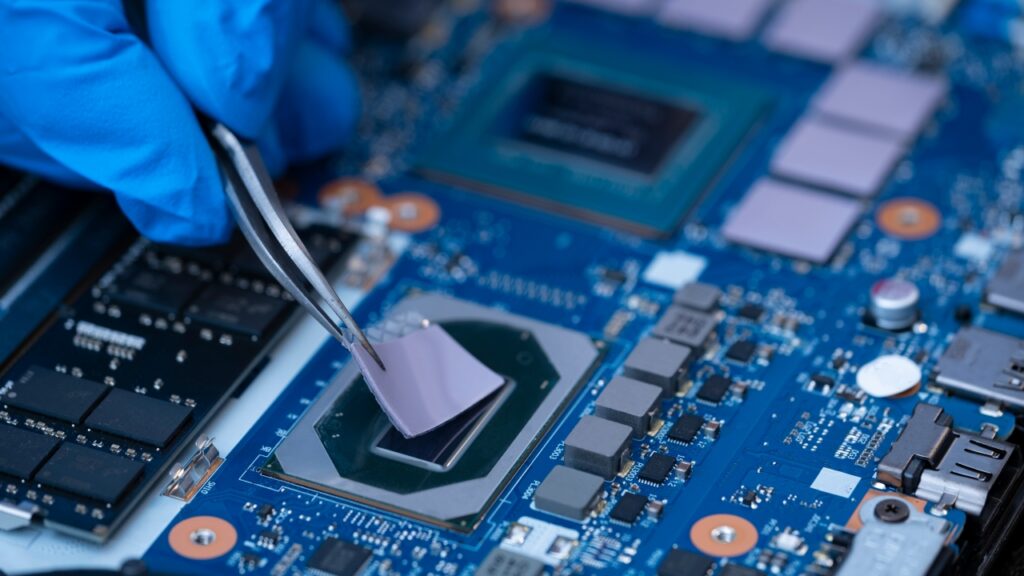

【4】プラズマ技術(Plasma Technology)

プラズマは、エッチング、成膜、表面処理の主役。

(1)プラズマとは

電子・イオン・中性粒子が混ざった「電離ガス」。

特性:

・ 高エネルギー反応

・ 表面化学を自在に制御

・ 反応の選択性が高い

・ 温度を上げずに加工できる

(2)プラズマエッチング

特徴:

・ 異方性加工(サイドウォールが垂直)

・ 高アスペクト比対応(100:1 超)

・ 選択性の制御

・ プラズマダメージを最小化する工夫が重要

AIチップの溝形状やTSV形成に不可欠。

(3)プラズマ成膜(PECVD等)

用途:

・ SiO₂

・ SiN

・ Low-k材料

・ パッシベーション膜

プラズマ特性(周波数、パワー、ガス組成)が膜質を決める。

(4)プラズマの最新技術

・ 原子層堆積用プラズマ

・ ダメージレスエッチング

・ 低エネルギーイオン制御

・ 高密度プラズマ(ICP)

・ プラズマ中の電荷ダメージ制御

装置メーカーのコア技術領域となっている。

【6】ガス制御・薬液制御技術

●ガス制御

・ MFC(Mass Flow Controller)

・ プレカーサ(ALD/CVD用)

・ 反応速度の微細制御

・ パーティクル管理

●薬液制御

・ HF、H₂O₂など高危険材料の管理

・ ウェットエッチング

・ 洗浄プロセス(SC-1/SC-2など)

ガスと液 の純度が歩留まりを左右する。

【7】装置連携とスマートファブ

工場は装置の集合体で動く。

最近は:

・ AI × 装置データ解析(FDC)

・ デジタルツインでの装置動作シミュレーション

・ 自動搬送システム(AMHS)との連携

・ リアルタイムプロセス制御(APC) が標準となりつつある。

装置技術は単体で存在せず、工場全体の最適化(Smart Fab)が必須。

【8】最新トレンド

・ 高NA EUVの実装

・ EUVマスクブラー対策

・ Stochastic defect の低減技術

・ 超高真空 × プラズマの複合装置

・ ALD × エッチングのハイブリッドプロセス

・ ガスのクリーン化(pptレベル)

・ 装置データのAI解析

特にEUV世代では、装置の限界=微細化の限界 と言えるほど重要性が高い。

【9】まとめ

・ EUV、真空、プラズマは先端デバイスの基盤技術

・ 装置性能が微細化(2nm → 1nm)を決める

・ 真空・温度・ガス制御が歩留まりを左右

・ Smart Fab 化が進み、AI活用が必須に

・ 装置技術の理解は半導体技術者にとって最重要スキル

【理解チェック】

1.EUV装置で真空環境が必須な理由は?

2.プラズマが半導体加工で使われる主な理由を2つ挙げてください。

3.高NA EUVが必要になる背景を説明してください。

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。