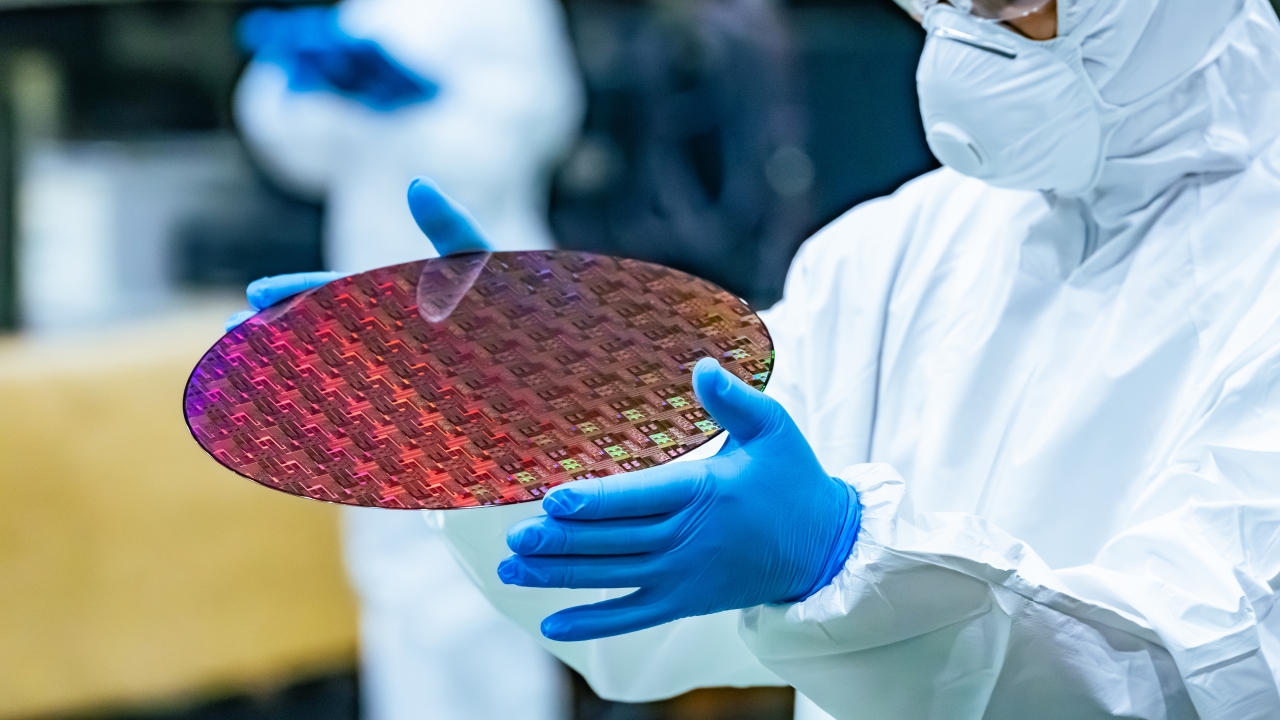

【1】ウェハ製造の役割と重要性

ウェハは半導体デバイスの土台となる材料で、

トランジスタや配線が形成される基板です。

● 平坦性

● 結晶品質

● 不純物濃度

● 欠陥密度

● 表面のクリーンさ

これらが 製品歩留まりと性能の90%を左右 するといわれるほど重要な工程です。

【2】ウェハ材料の種類

半導体のウェハには主に次の3種類が使われます。

■ シリコン(Si)

● 最も広く使われる材料

● コストが安く、成熟した技術

● CMOS、ロジック、メモリなど汎用

■ シリコンカーバイド(SiC)

● 高耐圧・高耐熱

● EVインバータ、産業用電源、太陽光パワコン

● 8インチウェハへ移行中(コストダウンの鍵)

■ ガリウムナイトライド(GaN)

● 高速・高周波に強い

● 通信、急速充電、データセンター向け

● 主にエピ層のみを形成する構造(Si基板上)

【3】シリコンウェハの製造工程(CZ法)

シリコンの単結晶を引き上げる代表的な方法が CZ(Czochralski)法 です。

流れは 以下の通り。

1.多結晶シリコンを坩堝で溶かす

2.種結晶(Seed Crystal)を接触させる

3.ゆっくりと引き上げながら結晶を成長

4.円筒状のインゴットが形成される

5.インゴットをスライスしてウェハに加工

6.研磨・洗浄して鏡面仕上げにする(CMP)

成熟したプロセスで、大口径(300mm)が量産。

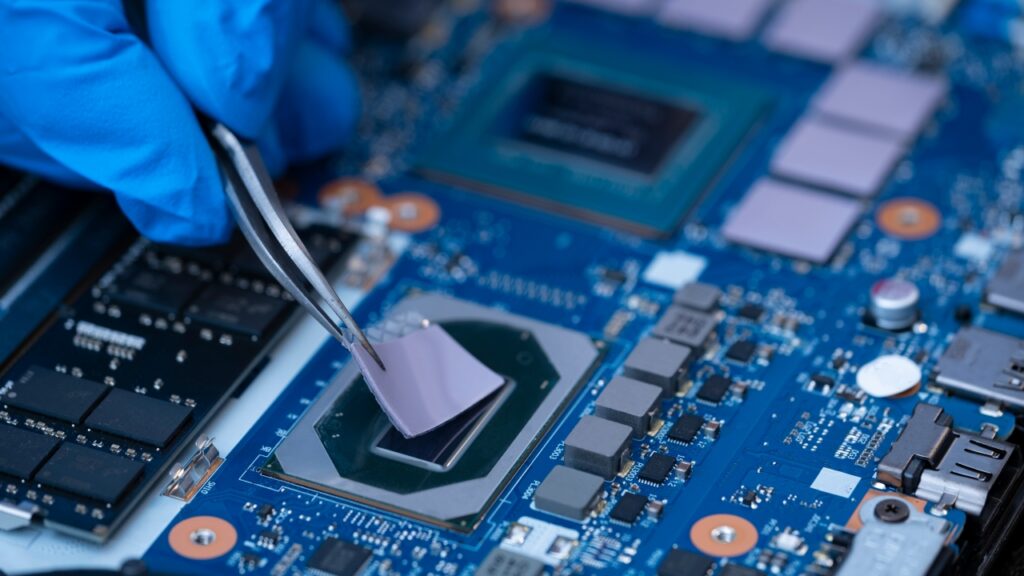

【4】エピタキシャル成長(Epitaxy: Epi)

エピタキシャル層は高品質な結晶層で、

トランジスタのチャネル特性や抵抗のばらつきを抑えるために使用されます。

● Siエピタキシ

● SiGeエピタキシ(高速・低電力向け)

● GaNエピ(通常はSi基板の上に形成)

使用する装置:

CVD炉(Epi炉)、MOCVD(GaN)

【5】SiCウェハの製造(昇華法)

SiCはシリコンよりはるかに硬い材料で、

単結晶の製造工程が全く異なります。

代表的な方法:

昇華法(Physical Vapor Transport:PVT)

1.高温(2000°C付近)でSiC原料を昇華させる

2.種結晶に蒸気が付着し結晶成長

3.厚いSiC単結晶が育つ

4.スライス → 研磨 → CMP

SiCは欠陥が入りやすいため、

近年は高品質化と大口径化(6 → 8インチ)が最大テーマ。

【6】GaNウェハの製造(主にエピ層形成)

GaNはSiCのように大口径単結晶が難しいため、

一般的に次の構造で使われます。

● Si基板の上にGaNエピ層をMOCVDで積層

● sapphire基板の上にGaNを成長

● SiC基板上GaN(高性能だが高コスト)

GaNの製造ポイント:

● 低欠陥密度

● 熱膨張差の吸収

● 高周波用途の特性向上

【7】ウェハ加工(スライス → 研磨 → 表面処理)

単結晶ができた後の工程を、テキストでシンプルに表現します。

1.インゴットをダイヤモンドブレードでスライス

2.ラッピング(粗研磨)

3.ポリッシング(鏡面研磨)

4.CMP(ナノレベルで平坦化)

5.超純水洗浄

6.クリーン検査(表面欠陥検査)

ウェハ表面の平坦性・清浄度は

最終的な回路性能に直結する要因です。

【8】品質管理の重要ポイント

ウェハ品質は後工程の歩留まりに直結します。

チェック項目:

● TTV(厚さばらつき)

● 表面粗さ(RMS)

● 結晶欠陥密度(epi defect density)

● パーティクル

● 金属コンタミ

● ボーリング(不純物濃度の均一性)

【9】まとめ

● ウェハは半導体製造の基礎体であり品質が歩留まりを左右する。

● Si、SiC、GaN は用途に応じた明確な使い分けがある。

● Si=汎用、SiC=高耐圧、GaN=高速・高周波。

● Epi層の品質はロジック・パワーデバイスどちらにも重要。

● SiCは大口径化、GaNは低欠陥化が現在の大テーマ。

【理解チェック】

1.CZ法とはどのような工程ですか?

2.SiCウェハが高価になる理由は?

3.GaNウェハが通常「エピ層構造」で使われる理由を説明してください。

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。