【1】なぜフリップチップが必要になったのか

ワイヤボンドでは:

・配線長が長い

・インダクタンスが高い

・高速信号に弱い

・I/O数の限界がある

といった問題が発生する。

しかし SoC・GPU・AIチップは:

・数千〜数万I/O

・超高速信号(GHz領域)

・大電流

・莫大な発熱

という圧倒的負荷がかかるため、ワイヤボンドでは対応できなくなった。

そこで登場したのが フリップチップ。

特長:

・配線長が最短 → 高速信号・低ノイズ

・I/O数を大幅増加

・電源/GNDを分散配置でき、電源品質向上

・放熱がチップ全面から可能

・高密度実装

結果、ハイエンドデバイスはほぼフリップチップに移行した。

【2】バンプ(Bump)構造の種類

フリップチップの性能を決める中心技術が、バンプである。

●(1)C4バンプ(従来型はんだバンプ)

材料:Sn-Ag-Cu(Pbフリー)

メリット:

・長年の実績があり信頼性が高い

・プロセスが成熟している

課題:

・微細ピッチ化に限界(<40 µmが厳しい)

・高電流用途では抵抗が増加

●(2)Cuピラー(Copper Pillar)

現在、最も急速に広がる方式。

構造:

Cu柱の先端に薄いSn層を形成 → リフローで接合

メリット:

・微細ピッチ(20–40 µm)対応

・高電流 × 高熱 × 高密度 に強い

・大規模AI/GPUで主流

課題:

・コプラナリティ制御が難しい

・Cu酸化を防ぐプロセスが必要

●(3)マイクロバンプ(HBM / 2.5D用)

特徴:

・10 µmクラスの超微細バンプ

・TSVと組み合わせて高帯域メモリHBMを形成

課題:

・1つの欠陥が“複数スタックの全滅”につながる

→ 歩留まりが圧倒的に重要

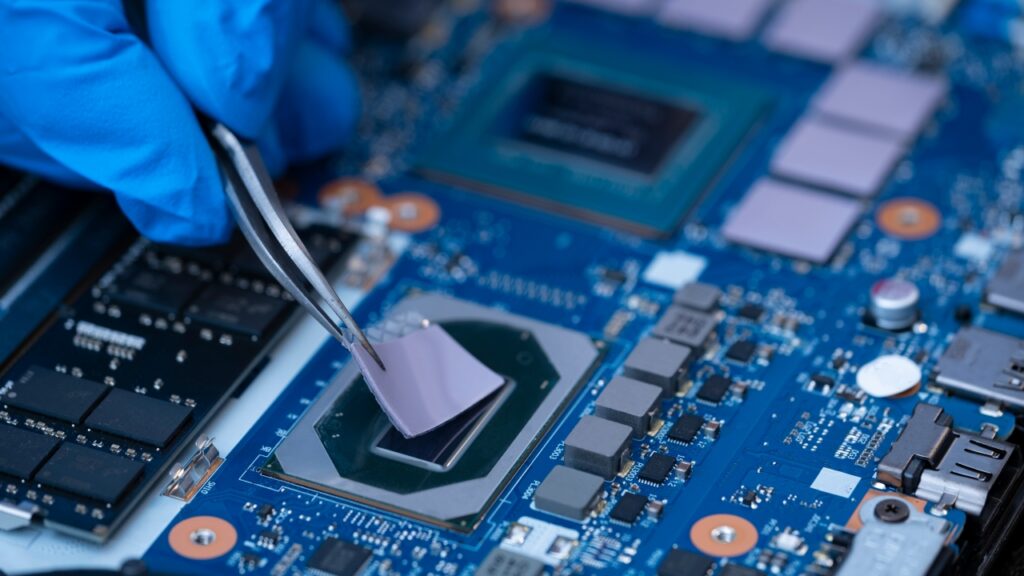

【3】アンダーフィル(Underfill)の役割

フリップチップは、チップと基板の熱膨張差が大きく、バンプが疲労・割れやすい。

この問題を解決するのが、アンダーフィル(樹脂)。

役割:

・熱サイクル応力の吸収

・落下衝撃の強化

・バンプ破壊の防止

・熱伝導パスの改善(高熱伝導UFも存在)

アンダーフィルの質が信頼性を左右するため、材料メーカーとの協業が必須。

【4】フリップチップの主な課題(実務視点)

●(1)コプラナリティ不良

バンプの高さばらつき → 接合不良

●(2)ボイド(Void)

アンダーフィル注入時の空洞 → クラック起点に

●(3)基板側パッドの汚染 / 酸化

→ 濡れ性不良で接合できない

●(4)熱問題

フリップチップはチップが表向きになるため、AIチップでは熱密度がボトルネックとなる。

●(5)高周波・電源ノイズ

バンプ配置でSI/PI/EMIが変動 → 解析とシミュレーションが必須

【5】フリップチップが主流になった理由

・高速信号に強い(配線長が最短)

・電源/GNDを面で取れる → 電源品質向上

・大I/O対応

・放熱が有利

・小型化に必須

・HBM・Chiplet・2.5D/3Dと相性が良い

特にGPU・AIチップ・HBMはフリップチップなしでは成立しないと言ってよい。

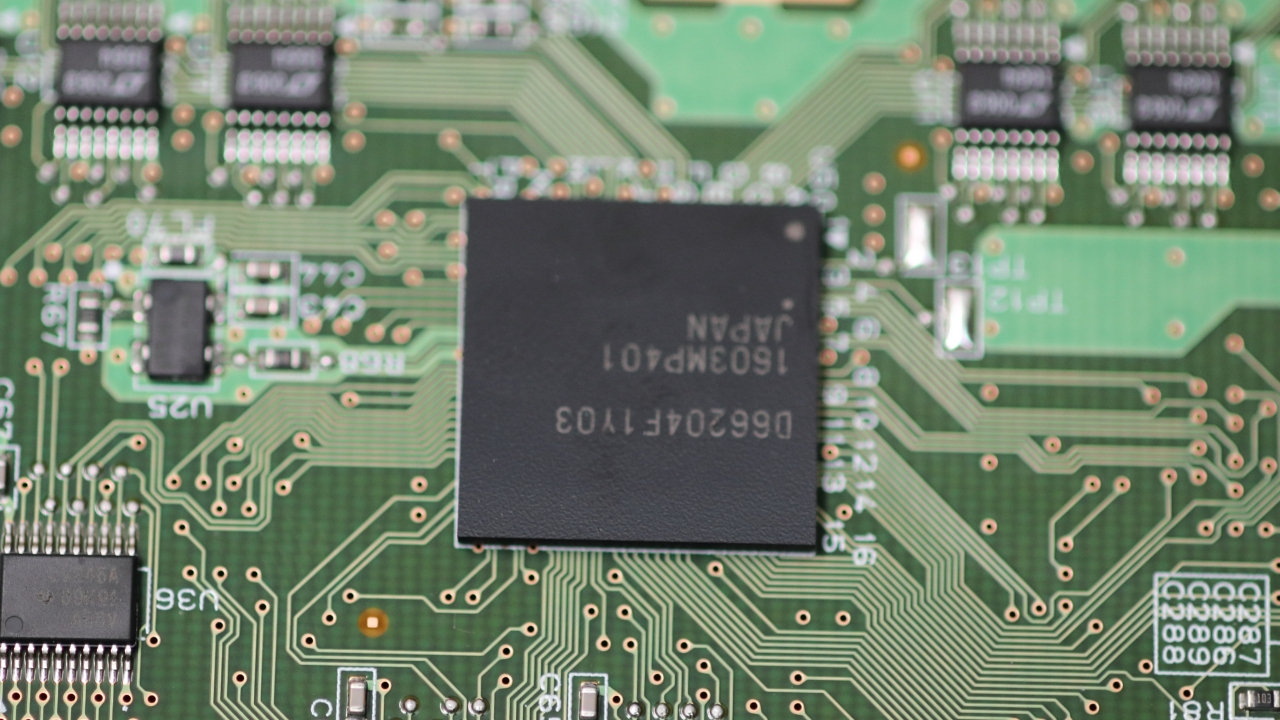

【6】製造プロセス(簡易フロー)

1.ウェハ上にUBM(下地金属)形成

2.バンプ形成(C4 / Cuピラーなど)

3.ダイシング

4.ピック&プレース

5.基板側とリフロー接合

6.アンダーフィル充填

7.モールディング

8.テスト

工程数は多く、歩留まりは複数工程に依存する。

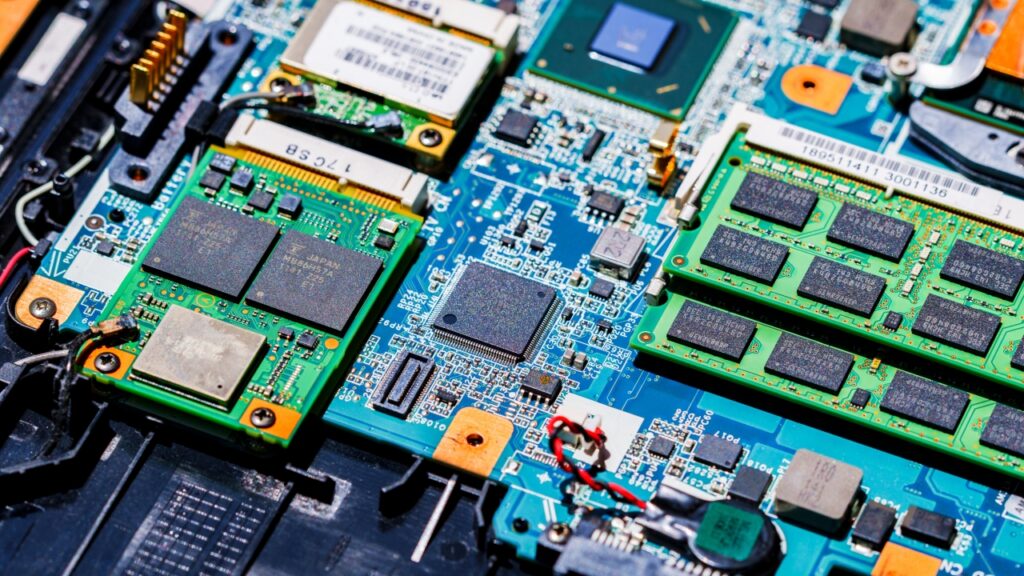

【7】最新トレンド

● Cuピラーの主流化

AI時代の電流量にCuがマッチ。

● 再配線層(RDL)との組み合わせ強化

Fan-out / 2.5D と統合。

● CoWoS / InFO など先端パッケージの基盤技術として強化

● 熱問題解決のためのTIM・ベイパーチャンバー併用

● マイクロバンプ → Hybrid bonding(直接接合)へのシフト

(TSMC・Intel・Samsungで進行)

【8】まとめ(6-2)

フリップチップは:

・高速 × 高密度 × 高熱

・大電流 × 大帯域 という先端要件に応える中心技術。

C4 → Cuピラー → マイクロバンプ → Hybrid bonding へと進化し、

HBM・AIチップ・Chiplet時代を支える基盤になっている。

【理解チェック】

1.フリップチップがワイヤボンドより高速信号に強い理由は?

2.Cuピラーが採用される主なメリットを1つ挙げよ。

3.アンダーフィルはなぜ必須なのか?

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。