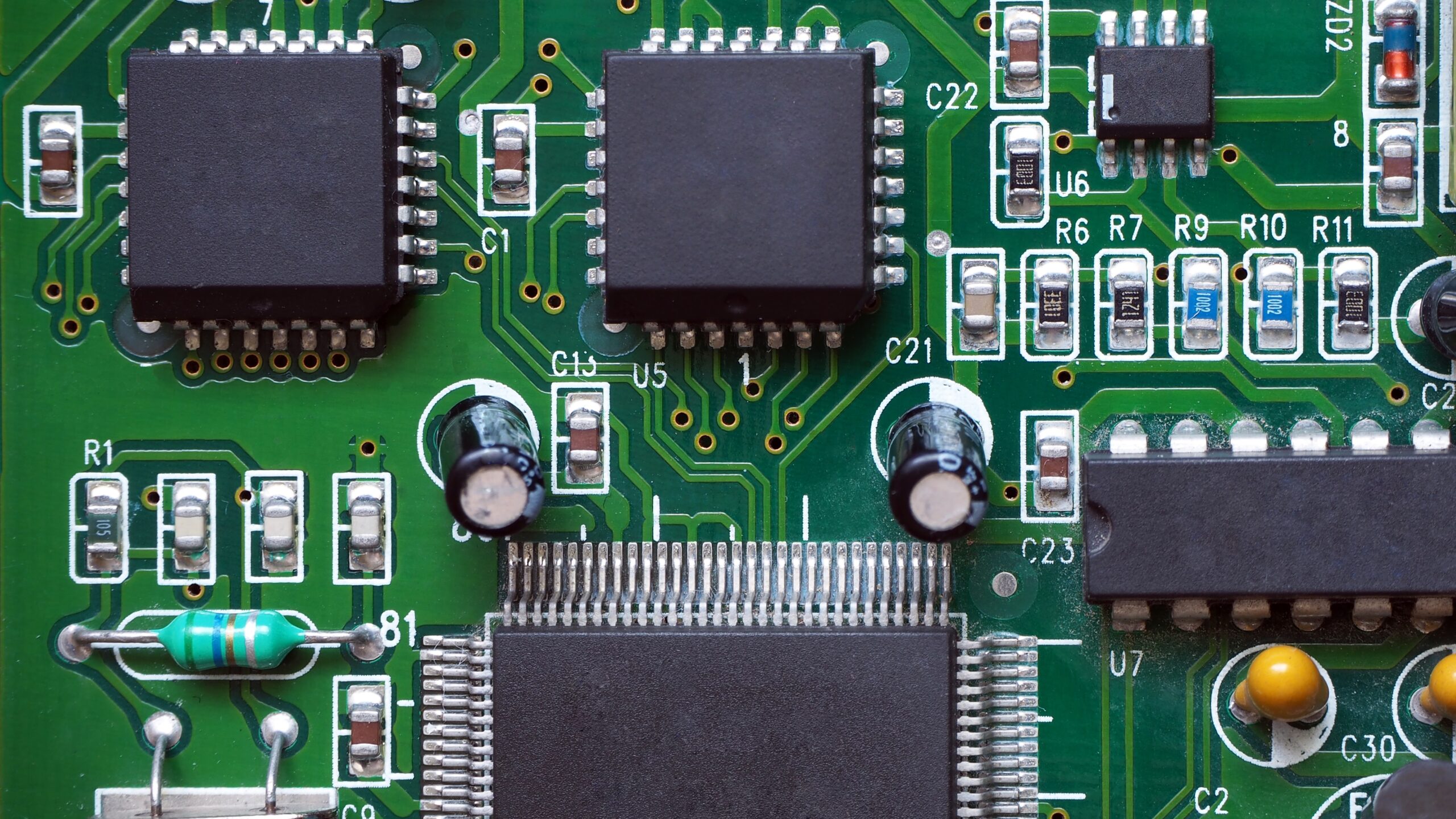

【1】実装(Assembly)とは何か

実装とは、パッケージ化された半導体チップをプリント基板(PCB)へ搭載し、電気的に接続して使える状態にする工程。

具体的には:

● 基板へはんだ付け

● リフローによる固定

● 接続不良の検査

● ボイド・クラック対策

● 熱・応力・EMIへの設計

最終製品(スマホ・車載ECU・サーバ・家電など)の性能・信頼性を決める重要工程。

【2】実装の全体フロー

一般的なフローは次の通り:

1.基板(Substrate / PCB)の準備

2.はんだペースト印刷(Stencil Printing)

3.チップ / パッケージ配置(Pick & Place)

4.リフロー炉で加熱・接続(Reflow)

5.X線・外観検査(AOI / AXI)

6.洗浄・保護処理(Underfill、Coating)

車載用や産業機器など、高信頼性が求められる製品では、チェック工程がさらに強化される。

【3】実装技術の要素

●(1)はんだペースト

Sn-Ag-Cu(SAC)系が主流。

粒径や粘度の違いが「印刷精度」に直結する。

課題:微細ピッチ化により

・ ブリッジ

・ ボイド

・ 濡れ不良 が発生しやすい。

●(2)ステンシル印刷

基板のパッド部に正確にはんだを載せる工程。

ポイントは:

・ ステンシル厚

・ 開口形状

・ 印刷圧

・ ペースト粘度

・ スキージ速度

印刷のわずかなズレが 接続不良→歩留まり低下 に直結する。

●(3)実装装置(Pick & Place)

チップを正確な位置に高速配置するロボット。

求められる性能:

・ μm単位の精度

・ 毎時数万点のスループット

・ ワーク認識のAI化

スマホは何百点ものパッケージが搭載されるため、実装ライン全体の最適化が重要。

●(4)リフロー(Reflow)

はんだを溶かして固着させる工程。

温度プロファイルは製品生命線:

・ 予熱

・ ソーク

・ リフロー(溶融)

・ クーリング

温度条件が悪いと

・ はんだ割れ

・ ボイド

・ ぬれ不足 が起こり、信頼性が著しく低下する。

●(5)アンダーフィル(Underfill)

フリップチップなどで使用。

はんだ接続部の応力を吸収し、信頼性を向上させる樹脂。

必要性が増している理由:

・ チップ薄型化で割れやすい

・ 熱膨張差の問題

・ はんだバンプの微細化

AI・5G向け高性能デバイスでは必須技術。

●(6)コンフォーマルコート(Coating)

湿度・塩害・埃から基板を守る保護膜。

車載・産業向けで重要。

【4】代表的な実装形態

● SMT(Surface Mount Technology)

→ 現代電子製品の主流方式

● THT(Through Hole Technology)

→ 電源基板など強度が必要な場合に使用

● PoP(Package on Package)

→ スマホでCPUとメモリを積む方式(3Dパッケージの一種)

● SiP(System in Package)

→ 複数チップを1モジュールに集積

実装はパッケージだけでなく、最終製品の小型化・省電力化に直結する技術 でもある。

【5】実装における故障モード

代表的な不良:

● はんだクラック

● ボイド

● ブリッジ

● 接続不良

● 基板反り

● アンダーフィル剥離

これらは車載要求(AEC-Q100など)では致命的であり、量産管理が非常に重要になる。

【6】近年の技術トレンド

● 微細ピッチ化(0201サイズなど)

● 高出力デバイス向けの放熱設計強化

● AI × 画像検査(AOI/AXI)による自動外観検査

● SiPによる高機能モジュール化

● 基板/樹脂/はんだ材料のアップデート

● フリップチップ実装の一般化

特に SiP・高放熱・高信頼性 が成長分野。

【7】まとめ

● 実装工程はチップを基板に取り付ける「最後の勝負どころ」

● はんだ印刷、配置、リフローが主要プロセス

● 信頼性確保にはアンダーフィルや保護コートが重要

● 微細化と発熱増により実装難易度は増している

● SiPや微細パッケージが今後の中心

【理解チェック】

1.リフロー炉で温度プロファイルが重要な理由を説明してください。

2.アンダーフィルはどのような時に必要になりますか?

3.実装における代表的な不良を3つ挙げてください。

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。