【1】最終テストとは何か

最終テスト(Final Test)は、完成した半導体チップやパッケージが、仕様どおりに動作するかを最終確認する工程。

不良を見逃すと、車載、安全機器、サーバなどで重大事故につながるため、

製品出荷の最終ゲート として非常に重要。

最終テストには2種類ある:

● E-Test(Wafer Test / ウェハプローブ)

● FT(Final Test / パッケージ後テスト)

【2】E-Test(Wafer Test)とは

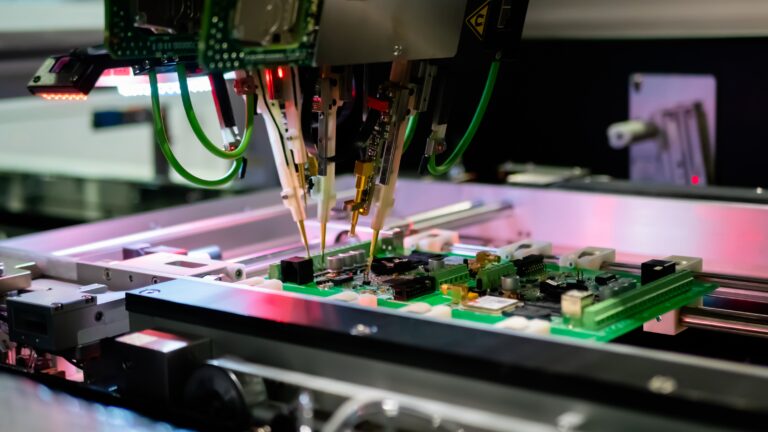

ウェハ上で個々のチップにプローブ針を当てるテスト。

●目的

・ チップの電気的基本特性を測定

・ 不良チップを選別(KGD:Known Good Die の確保)

・ 製造プロセスの品質フィードバック

●主な測定項目

・ トランジスタの特性(Id-Vg、リーク)

・ 抵抗値、容量

・ 発振テスト

・ メモリビットの基本動作

・ スピードパス(タイミング)

●使用機器

・ ウェハプローバ(Probe Station)

・ テスター(ATE:Automatic Test Equipment)

・ 高倍率カメラ/アライメントシステム

E-Testで不良を排除することで、後工程の無駄なコストを抑えることができる。

【3】FT(Final Test)とは

パッケージ完成後の最終検査。

●目的

・ 出荷レベルの性能確認

・ I/Oの接続確認

・ 熱・電気ストレスに対する信頼性確認

・ 車載規格(AEC-Q100など)への適合

●主な測定項目

・ 高速I/O(PCIe、DDR、SerDes)

・ 消費電力(電源特性)

・ クロック速度(最大周波数)

・ 機能テスト(ロジック動作、メモリ動作)

・ 温度サイクルでの安定性

・ バーンイン(加速試験)

特にAIサーバ用GPUや高速メモリでは、熱試験・ストレス試験が必須。

【4】バーンイン(Burn-in)試験

最も重要な信頼性試験のひとつ。

●バーンインとは

高温・高電圧などのストレス環境で一定時間動作させ、

初期故障(Infant Mortality)を検出する試験。

●なぜ重要か

半導体故障は「バスタブ曲線」で説明され、

初期故障期に不良が多発するため、

出荷前に潰しておく必要がある。

【5】検査自動化とAI活用

近年、テスト量が爆発的に増加(特にAI半導体)。

そのため:

● テストプログラムの自動生成

● データ解析によるパス/フェイル判定

● 画像AIによるプローブマーク判定

● 不具合因果をAIが推定するツール

などが急速に普及している。

テスト工程は今後、AI主導の品質保証 へ移行していくと予測される。

【6】テストコストと歩留まりへの影響

テストは工程の中でもコストが高い。

理由は:

● 高価なATE装置(1台 数億〜数十億円)

● 時間あたりテスト量に制限がある

● 消費電力上昇により高負荷テストが増えた

● メモリ容量の増大でテスト時間が伸びている

したがって、テスト効率の改善は歩留まり改善と利益率の鍵 となる。

【7】最新トレンド

● チップレット化によるテスト工程の複雑化

● 3Dパッケージ(HBM)の温度テスト需要増

● 低電圧化により測定精度が重要に

● マルチサイト・並列テストの技術向上

● 高速通信規格(112Gbps級)のテスト装置進化

● ウェハレベルバーンインの研究

特にAIデバイスは発熱が大きく、温度+電気的ストレスの複合テストが必須 になっている。

【8】まとめ

● E-Test はウェハ段階の基本特性検査

● FT はパッケージ後の最終出荷テスト

● バーンインは初期故障の検出に必須

● テストは装置・時間が高コストな工程

● AI × テストデータ解析が必須の時代へ

【理解チェック|4-13】

1.E-Test と Final Test の最大の違いは?

2.バーンイン試験が必要な理由を説明してください。

3.テスト工程が「高コスト」と言われる理由を2つ挙げてください。

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。

![[半導体シリーズ] Vol.3/4 ― 半導体産業を支える技術と仕組み<br>検査・サプライチェーン・環境への取り組み](https://otis-group.com/wp-content/uploads/2025/12/column_251229-1024x576.jpeg)