【1】なぜ先端パッケージが重要になったのか

AIやデータセンター向け半導体では、以下のような要求が急速に高まっている。

主な要求:

・高いメモリ帯域

・高速チップ間通信

・高発熱への対応

・小型化

これらを実現するためには、単一チップの性能だけではなく、複数チップを効率よく接続するパッケージ技術が不可欠となる。

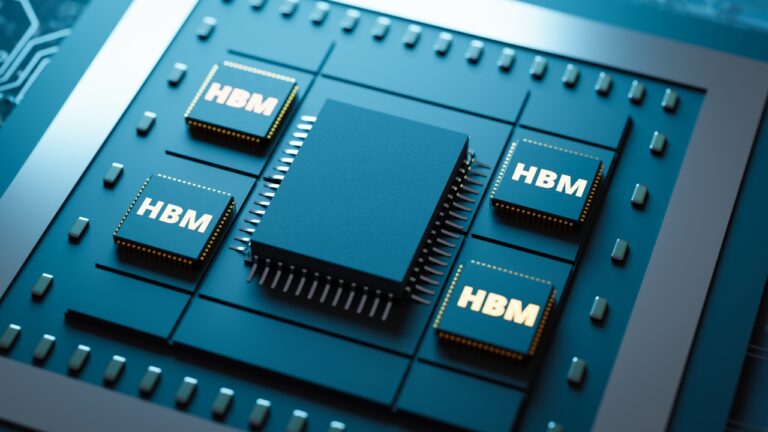

【2】2.5Dパッケージ

2.5Dパッケージでは、シリコンインターポーザと呼ばれる基板上に複数のチップを配置する。

構造の特徴:

・チップを横方向に配置

・シリコン配線で接続

・高密度配線が可能

この方式は、GPUとHBMメモリの接続などで広く使われている。

代表例:

・TSMC CoWoS

・Samsung I-Cube

AIチップでは、HBMメモリを高速に接続するために2.5Dパッケージが重要な技術となっている。

【3】3Dパッケージ

3Dパッケージでは、チップを垂直方向に積層することで、より高い集積度を実現する。

主な技術:

・TSV(Through Silicon Via)

・ハイブリッドボンディング

・ダイスタッキング

これにより、チップ間の距離を極端に短くすることができ、通信速度と電力効率を向上させることができる。

代表例:

・Intel Foveros

・TSMC SoIC

【4】Fan-Outパッケージ

Fan-Outは、再配線層(RDL)を用いて配線密度を高めるパッケージ技術である。

特徴:

・インターポーザ不要

・薄型化が可能

・高密度配線

スマートフォン向けプロセッサなどで広く採用されている。

代表例:

・TSMC InFO

・Samsung eWLB

【5】先端パッケージが半導体性能を決める時代

AIチップでは、チップ単体よりもパッケージ構造全体が性能を決めるケースが増えている。

特に重要な要素:

・チップ間通信速度

・メモリ帯域

・熱設計

・電力供給

つまり半導体の性能は、トランジスタ設計だけでなく、パッケージ・材料・実装技術の総合力によって決まる時代になっている。

この流れは、材料メーカーや加工技術を持つ企業にとっても重要な意味を持つ。

【まとめ(10-5)】

・先端パッケージは半導体性能を左右する重要技術

・2.5D・3DパッケージがAIチップで広く採用

・HBM接続で2.5D技術が重要

・パッケージ設計がシステム性能を決める時代

【理解チェック】

1.なぜAIチップでは先端パッケージが重要なのか?

2.2.5Dパッケージと3Dパッケージの違いは何か?

3.半導体性能においてパッケージ技術が重要になる理由は

コラム監修:角本 康司 (オーティス株式会社)

語学留学や商社での企画開発を経て2011年にオーティス株式会社入社。経営企画部を中心に製造・技術部門も兼任し、2018年より代表取締役として事業成長と組織強化に努めている。

※本記事は教育・啓発を目的とした一般的な技術解説であり、特定企業・製品・技術を示すものではありません。

![[半導体シリーズ] Vol.3/4 ― 半導体産業を支える技術と仕組み<br>検査・サプライチェーン・環境への取り組み](https://otis-group.com/wp-content/uploads/2025/12/column_251229-1024x576.jpeg)